## A Quartz Watch Time Base Monitor

By George P. Vella-Coleiro AT&T Bell Laboratories

The circuit described here was developed to enable the frequency of oscillation of a quartz watch time base to be measured accurately in a non-invasive manner. Most digital watches on the market today use a quartz oscillator with a frequency of 32.768 kHz (2<sup>15</sup>Hz) which is capable of great precision. The less expensive watch models, however, are typically adjusted at the factory to only ±30 s/month. Using the circuit described here and a simple frequency counter, it is possible to adjust a quartz watch to an accuracy of ±1 s/year.

The problem with monitoring the frequency of a quartz watch arises from the very low power nature of the circuit. This means that even a high-impedance probe produces an excessive amount of loading. This problem is circumvented by using the acoustical energy emitted by the crystal. As might be expected, the acoustical power is minute, resulting in two difficulties that need to be overcome: interference and noise.

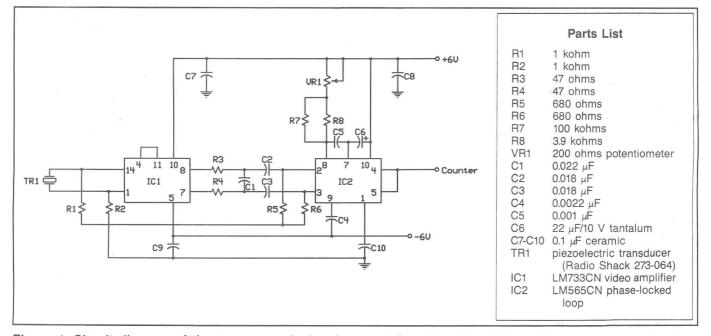

In the circuit shown in Figure 1, the problem of interference is taken care of

by using a differential video amplifier (IC1) with good common mode rejection to amplify the weak signal picked up by the ultrasonic microphone (a piezoelectric transducer). This amplifier has a voltage gain of approximately 400, which is adequate to drive the input of phaselocked loop (PLL) IC2. The PLL takes care of the second problem, noise, by means of a loop filter with a long time constant. This effectively produces a very narrow noise bandwidth.

A PLL was chosen for this application instead of a narrow-band filter tuned to 32.768 kHz in order to avoid the problem of drift of the center frequency of the filter. It is estimated that achieving an adequate signal-to-noise ratio would require a filter with a bandwidth less than 1 Hz, necessitating a center frequency stability on the order of one part in 10<sup>5</sup>. This level of stability is achievable through temperature compensation of the components that determine the center frequency, together with temperature control, but a PLL provides a much simpler solution. The frequency of oscillation of the voltage-controlled

oscillator (VCO) in a well-designed PLL is locked to the frequency of the received signal, and the only requirement is that this frequency be within the capture range of the PLL.

A simple second-order loop filter, formed by C6 and a 3.6 kohm resistor internal to IC2, has been found to be entirely satisfactory for this application. The time constant was made large (about 0.1 s) so as to enhance immunity to noise and out-of-band signals. This was done at the expense of lock-up time and capture range, which are relatively unimportant in this application.

In Figure 1, video amplifier IC1 is

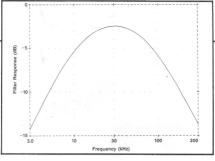

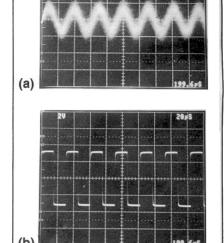

configured for its maximum gain of 400, resulting in a bandwidth of 40 MHz. This bandwidth is limited to a much narrower range, centered around 30 kHz, by an R-C filter consisting of R3-R6 and C1-C3 before being applied to the input of PLL IC2. The simulated frequency response of the filter, including the output resistance of IC1 and the input resistance of IC2, is shown in Figure 2, indicating a 3 dB bandwidth of 10 kHz to 90 kHz. Figure 3(a) shows the watch signal

Figure 1. Circuit diagram of the quartz watch time base monitor.

obtained at the input of IC2 (pins 2 and 3) with IC2 removed from the circuit to avoid any pickup of the VCO output. The waveform at the output of IC2 (pin 4) with the PLL locked to the watch frequency is shown in Figure 3(b).

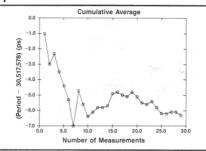

The free-running frequency of the VCO is adjusted by means of VR1 to within a few hundred hertz of 32.768 kHz in order to bring the frequency of the quartz oscifator within the capture range of the PLL. The watch is then placed atop the transducer, and the output of the VCO, monitored at pin 4 of IC2, becomes locked to the frequency of the quartz oscillator. The period rather than the frequency of the VCO is monitored by the counter in order to reduce the measurement time required to achieve the desired resolution. In a typical measurement, the counter is set to average 105 periods (the largest number available on the author's counter) and for a display where the least significant digit is 1 ps. This corresponds to a timing deviation of approximately 1 s/year. Successive readings of the counter fluctuate by several picoseconds, but averaging a number of readings reduces the fluctuations. A set of data where successive readings were averaged is shown in Figure 4. The abscissa shows the number of readings averaged, and the ordinate shows the average period expressed as a difference from the ideal value of 30,517,578 ps. A deviation of 1 ps corresponds to a timing error of approximately 1 s/year. Averaging 10 readings is sufficient to yield a measurement stable to better than ±1 ps, enabling the watch time base to be set to within 1 s/year.

The watch for which the data in Figure 4 were taken, an inexpensive model,

Figure 2. Simulated frequency response of the filter.

Figure 4. Period of oscillation of a quartz watch time base after adjustment.

gained about 4 s/week before adjustment. Since the frequency counter's time base was not calibrated to the required degree of accuracy (three parts in 108), the watch's drift rate was determined by comparison with standard time signals over a period of a few weeks. The requisite fractional change in period was then made using the frequency counter readings as relative rather than absolute measurements. After adjustment, the watch has gained less than 2 seconds in 3 months. Not bad for a timepiece costing less than \$20!

The fact that a miniaturized, low power, inexpensive watch circuit can achieve such a high degree of accuracy is a tribute to the sophistication of modern integrated circuit technology.

Figure 3. Waveforms observed at (a) the input of IC2(pins 2 and 3): and (b) the output of IC2 (pin 4).

Undoubtedly, the frequency will drift over a period of several months, but the circuit described above is simple enough to use that adjustments can be made as needed to maintain the desired precision.

## About the Author

George P. Vella-Coleiro is with AT&T Bell Laboratories in Murray Hill, NJ 07974, where he supervises development of InP-based optoelectronic integrated circuits for fiber communications. His time base monitor design won one of the runner-up prizes in the 1989 RF Design Awards Contest. Mr. Vella-Coleiro can be reached at (201) 582-3381.

## Announcing: The Fifth Annual RF Design Awards Contest Grand Prize: Advantest R3261A Spectrum Analyzer

## Contest Entry Rules

- 1. Entries shall be RF circuits containing no more than eight single active devices, or six integrated circuits, or be passive circuits of comparable complexity.

- 2. The circuit must have an obvious RF function and operate in the below-3 GHz frequency range.

- 3. Circuits must be the original work of the entrant, not previously published. If developed as part of the entrant's employment, entries must have the employer's approval for submission.

- 4. Components used must be generally available, not obsolete or proprietary.

- 5. Submission of an entry implies permission for RF Design to publish the material. All prize-winning designs will be published, plus additional entries of merit.

- 6. Winners shall assume responsibility for any taxes, duties, or other assessments which result from the receipt of their prizes.

- 7. Entry must be postmarked no later than March 31, 1990, and received no later than April 10, 1990.

Send entries to: RF Design Awards Contest RF Design Magazine 6300 S. Syracuse Way, Suite 650 Englewood, Colorado 80111